美光科技正式揭幕位於台中的DRAM後段封裝與測試廠,象徵在台垂直整合前段晶圓製造以及後段組裝與測試佈局完成。美光並強調,台灣已是美光最大的DRAM製造基地...

美光科技(MicronTechnology)正式揭幕位於台中的DRAM後段封裝與測試廠,不僅象徵在台DRAM卓越中心的佈局完成,同時垂直整合位於桃園和台中的前段晶圓製造以及後段組裝與測試。美光科技總裁兼執行長Sanjay Mehrotra並強調,台灣已經成為美光最大的DRAM製造基地。

美光科技在台新落成的台中後段封測廠及DRAM卓越中心總投資金額估計高達新台幣500億元,預計將創造500到1,000個就業機會。美光科技總裁兼執行長Sanjay Mehrotra表示,美光科技已是台灣最大的外資與外商雇主,如今隨著台中DRAM後段封測廠的開幕,將使其在台員工數增加達到7,000人以上,同時也象徵美光持續致力於台灣半導體生態系統的長期承諾。

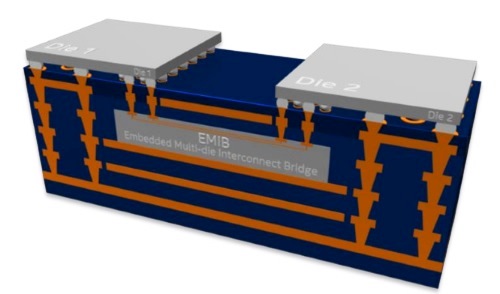

台中DRAM後段封測廠將著重於3D IC、TSV等高價值的產品封裝,未來並將持續提升品質與工程能力,增加更多其他高價值產品的封裝。

美光在台灣的DRAM後段封測廠啟用,完成DRAM卓越中心佈局

美光在台灣的DRAM後段封測廠啟用,完成DRAM卓越中心佈局

Mehrotra看好DRAM市場長期結構穩健,供需平衡。從需求面來看,DRAM市場日趨多元化,主要的需求推動力道來自於PC、行動、繪圖以及伺服器與雲端運算等領域。而在供應面,隨著業界廠商對於新技術轉型的投入日益困難,加上資本集中,執行力度越來越具有挑戰性。但他預計今年DRAM供應約有20%的成長,從整體來看,供需大致上仍能保持均衡。

針對近來中美貿易戰升溫,是否會對記憶體供應鏈發展造成影響?Mehrotra表示,從全球供應鏈的角度來看,目前首當其衝的是DRAM模組。「DRAM模組是DRAM封裝測試的最後組裝階段,成為供應鏈中最受影響的部份。」為此,美光將因應加徵關稅需求,相應地調整在台灣和全球的封測組裝廠,協助客戶因應關稅衝擊。

至於DRAM晶圓製造則不受影響或增加產量。他強調,「台灣(包括桃園和台中廠)已經是美光最大的DRAM製造廠。美光的DRAM需求主要來自日本,但由於在中國沒有DRAM製造廠,因此在DRAM晶圓製造方面不至於受到影響。」儘管並未規劃增加晶圓產量,但美光科技將持續投入技術開發與升級,以提高記憶體單元的成長。

針對製程技術規劃,美光科技預計每年將引進一代新製程,目前桃園廠與台中廠已在量產1x製程,桃園廠今年引進了1y製程,預計明年量產,台中廠將在明年引進1z製程,預計2020年之後量產。